Источник: atmega8.ru

Интерфейс Serial Peripheral Interface (SPI) предназначен для обмена данными с переферийными устройствами (LCD экраны, карты памяти и т.д).

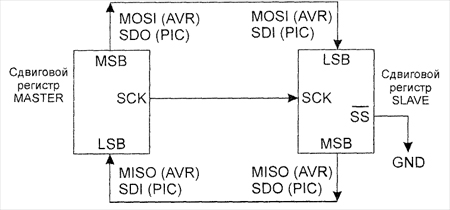

При обмене данными по этому интерфесу микроконтроллер ATmega8 работает в режиме ведущего устройства (MASTER), к которому можно подключить 1 или несколько ведомых блоков (SLAVE). Передача данных начинается, когда ведомое устройство активизируется ведущим по линии /SS. Передача данных происходит следующим образом:

- Ведущее устройство записывает байт, подлежащий передаче, в сдвиговый регистр SPDR

- При каждом тактовом импульсе (тактовые импульсы задаются выходом SCK) ведущее устройство перемещает 1 бит данных на выход MOSI, а ведомое устройство одновременно передаёт 1 бит данных на вход MISO ведущего. Таким образом за 8 тактовых импульсов устройства Master и Slave обмениваются 1 байтом данных

- По окончании передачи данных в регистре SPCR устанавливается флаг запроса на прерывание

Текущая передача данных может быть преждевременно завершена подачей в линию SS логической единицы.

Схема передачи данных по SPI:

К микроконтроллеру atmega8 можно подключить несколько ведомых устройств. Активным будет тот, на вход SS которого подан лог.0. Пример подключения нескольких SLAVE блоков к микроконтроллеру:

В Atmega8 выходы SPI расположены на порту B: B2 - линия SS, B3 - MOSI, B4 - MISO, B7 - SCK

Регистры управления и состояния SPI в Atmega8

Регистр управления SPCR

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 |

SPIE=1 : прерывание по завершению передачи данных по SPI разрешено

SPE=1 : активация интерфейса SPI. При поступлении сигнала сброса SPE переводится в состояние лог.0 и интерфейс SPI отключается

DODR=1: первым передаётся младший разряд байта данных. При DODR=0 первым передаётся старший разряд байта данных

MSTR=0 - atmega8 определяется как ведомое устройство (SLAVE). MSTR=1 - микроконтроллер с интерфейсом SPI определяется как ведущее устройство. Если линия SS (вывод 2 порта B) настроена в качестве входа, то при низком уровне сигнала на этой линии MSTR сбрасывается в лог.0

CPOL=1 - на линии SCK в неактивном состоянии находится сигнал высокого уровня. С помощью этого разряда, а также разряда CPHA устанавливается один из четырёх возможных режимов передачи данных.

SPR0, SPR1 предназначены для выбора частоты тактирования на линии SCK (в режиме Master). Если микроконтроллер работает в режиме SLAVE, то эти регистры не имеют никакого значения

Выбор режима работы SPI:

| CPOL | CPHA | Режим работы SPI |

| 0 | 0 | MASTER переводит линию SS в состояние лог.0. По ниспадающему фронту сигнала соответствующий ведомый блок включается в обмен данными. Передача начинается с того, что устройство MASTER помещает в свой регистр SPDR байт, подлежащий передаче. После 8-го тактового импульса линии SCK передача завершается, в регистрах SPSR устанавливается флаг SPIF. Одновременно со сбросом линии SS в исходное состояние (лог.1) ведущее устройство завершает передачу, ведомое устройство становится неактивным |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

Выбор частоты тактирования на линии SCK:

| SPR1 | SPR0 | Частота SCK |

| 0 | 0 | Тактовая частота микроконтроллера / 4 |

| 0 | 1 | Тактовая частота микроконтроллера / 16 |

| 1 | 0 | Тактовая частота микроконтроллера / 64 |

| 1 | 1 | Тактовая частота микроконтроллера / 128 |

Регистр состояния SPSR

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| SPIF | WCOL | - | - | - | - | - | - |

Флаг WCOL устанавливается в случае, когда во время передачи данных предпринимается попытка записи в регистр данных SPI

Флаг SPIF указывает на завершение передачи и вызывает запрос на прерывание (если прерывания разрешены)

Пример работы с SPI в atmega8:

{

SPCR = 0x52;

SPSR = 0x00;

}

unsigned char SPI_transmit(unsigned char data)

{

SPDR = data;

while(!(SPSR & (1<<7)));

data = SPDR;

return(data);

}

unsigned char SPI_receive(void)

{

unsigned char data;

SPDR = 0xff;

while(!(SPSR & (1<<7)));

data = SPDR;

return data;

}