Source: Wikipedia

MOS Technology 6502, или просто 6502, — восьмиразрядный микропроцессор, разработанный компанией MOS Technology в 1975 году. В момент появления на рынке он был дешевле аналогичных изделий компаний-конкурентов (Motorola и Intel). Несмотря на это, а также низкую тактовую частоту, в среднем он показывал сходную с ними производительность за счёт продуманных способов адресации памяти, коротких циклов исполнения команд и некоторой конвейеризации. Появление таких процессоров, как 6502 и Zilog Z80, в конечном счёте предопределило появление домашних компьютеров в конце 1970-х годов. Архитектура 6502 была лицензирована компаниями Rockwell, Synertek и многими другими, и использована во многих разработках. Процессор 6502 и его модификации до сих пор применяются во встраиваемых системах.

Микросхема 6502 datashet - тут и тут и тут

Микросхема 6532 datashet - тут

Сопроцессор 6800 datashet - тут

Пример 2

Приложение №1. Система команд 6502.

Источник тут

Рассмотрим систему команд архитектуры 6502. В Денди используется именно эта модель, за исключением блока десятичной арифметики.

Процессор оперирует целыми восьмиразрядными числами. Содержит всего 6 программно-доступных регистров. Из них 5 – восьмиразрядных, и 1 – шестнадцатиразрядный программный счетчик.

A – регистр - аккумулятор. Как и большинство «простых» архитектур – 6502 является «аккумуляторной», то есть во всех, или почти во всех, операциях явно или неявно участвует аккумулятор.

PC – программный счетчик. Единственный 16-ти разрядный регистр – указатель выполняемой команды (классически).

S – регистр - указатель вершины стека (первой свободной ячейки). Стек находится в пространстве адресов 0100h – 01FFh и «растёт» от старшего к младшему.

P – регистр флагов.

P[0] - “C” – “Carry” – флаг переноса из старшего разряда (классически).

P[1] - “Z” – “Zero” – признак нулевого результата (классически).

P[2] - “I” – “Interrupt” – флаг маскирования прерывания аппаратного прерывания на линии IRQ – варьируется командами SEI/CLI.

P[3] - “D” – “Decimal” – флаг режима десятичной арифметики. Так как в Денди этот режим отсутствует, то этот флаг не используется процессором, может использоваться программистом. Варьируется командами SED/CLD.

P[4] - “B” – “Break” – флаг программного прерывания (команда BRK).

P[5] - “ 1”

P[6] - “V” – “” – флаг переноса в знаковый разряд (из 6-ого в 7-ой - классически).

P[7] - “N” – “” – флаг знака результата операции – дублирует седьмой разряд (классически).

X, Y – регистры индексной адресации (или просто "общего назначения").

В общем итоге получается регистров для "юзания" всего навсего 3 (A,X,Y) - да и то, многие команды жестко привязаны именно к одному из них, очень часто неудобно бывает, что рождает лишние мнемоники и обращения в память.

Напомним, что система команд процессора оперирует или с перечисленными выше регистрами, или с адресным пространством памяти (64кб) – все устройства, управляемые процессором, должны отображаться своими регистрами на память.

И так – о способах адресации памяти.

ABS - прямая, в команде указывается полный 16-разрядный адрес операнда:

ABS, X (ABX)- индексированная по X, указывается базовый 16-разрядный адрес, к которому прибавляется смещение из регистра X;

ABS, Y (ABY) - индексированная по Y, указывается базовый 16-разрядный адрес, к которому прибавляется смещение из регистра Y.

АСС - аккумуляторная, подразумевает наличие операнда в регистре A процессора (что требуется указать в мнемонике).

IMM - непосредственная, 8-разрядный операнд расположен сразу за кодом команды (в мнемонической записи перед непосредственным операндом ставится символ «#»).

IMPL - неявная (указывается лишь мнемоника), операнды не указываются – жесткая логика работы инструкции.

IND - косвенная, задается адрес ячейки памяти, в которой хранится адрес операнда - бывает следующих видов:

IND, X (NDX) - индексно-косвенная, указывается 8-разрядный адрес в нулевой странице (в квадратных скобках), к которому прибавляется содержимое регистра X, после чего из ячейки памяти с вычисленным адресом и следующей за ней извлекается полный 16-разрядный адрес операнда (в мнемонике после адреса через запятую ставится и "X"). Другими словами - в области нулевой страницы создается таблица адресов, а при помощи переменной в регистре "X" можно по ним "бегать";

IND, Y (NDY) - косвенно-индексная, указывается 8-разрядный адрес в нулевой странице (в квадратных скобках), после чего из заданной ячейки памяти и следующей за ней считывается 16-разрядный базовый адрес, к которому прибавляется содержимое регистра Y, и из ячейки с вычисленным адресом извлекается операнд (в мнемонике после адреса через запятую ставится и "Y"). В данном случае переменная в регистре "Y" играет роль смещения относительно адреса базы, хранящегося в нулевой странице;

REL - относительная, в команде указывается 8-разрядное смещение относительно содержимого счетчика команд PC;

ZP - адресация нулевой страницы, в команде задается 8-разрядный адрес, определяющий ячейку памяти нулевой страницы, где хранится операнд;

ZP, X (ZPX) - индексированная по X адресация нулевой страницы, указывается 8-разрядный базовый адрес в нулевой странице, к которому прибавляется содержимое регистра X, и из ячейки памяти с вычисленным адресом извлекается операнд;

ZP, Y (ZPY) - индексированная по Y адресация нулевой страницы, в нулевой странице указывается 8-разрядный базовый адрес, к которому прибавляется содержимое регистра Y, и из ячейки памяти с вычисленным адресом извлекается операнд.

Ниже приведем саму систему команд (Всего 56 мнемоник инструкций).

|

Мнемоника |

Краткое описание |

Методы адресации |

Запись на языке ассемблера |

Код команды |

Число байтов |

Изменяемые флаги |

|

ADC |

Сложение с учетом флага переноса: А + d8 + С. Результат в аккумуляторе А и флаге переноса C |

IMM |

ADC #d8 |

69 d8 |

2 |

V, N, Z, С |

|

ZP |

ADC 08 |

65 a8 |

2 |

|||

|

ZP, X |

ADC а8, X |

75 a8 |

2 |

|||

|

ABS |

ADC а16 |

6D a16l a16h |

3 |

|||

|

ABS, X |

ADC а16, Х |

7D a16l a16h |

3 |

|||

|

ABS, Y |

ADC a16, Y |

79 a16l a16h |

3 |

|||

|

|

ADC (a8, X) |

61 a8 |

2 |

|||

|

|

ADC (a8), Y |

71 a8 |

2 |

|||

|

AND |

Поразрядное логическое И аккумулятора и операнда |

IMM |

AND #d8 |

29 d8 |

2 |

N, Z |

|

ZP |

AND a8 |

25 a8 |

2 |

|||

|

ZP, X |

AND a8, X |

35 a8 |

2 |

|||

|

ABS |

AND a16 |

2D a16l a16h |

3 |

|||

|

ABS, X |

AND a16, X |

3D a16l a16h |

3 |

|||

|

ABS, Y |

AND a16, Y |

39 a16l a16h |

3 |

|||

|

IND, X |

AND (a8, X) |

21 a8 |

2 |

|||

|

IND, Y |

AND (a8), Y |

31 a8 |

2 |

|||

|

ASL |

Арифметический сдвиг операнда влево, без начального учета флага C (умножение на 2) |

ACC |

ASL A |

0A |

1 |

N, Z, C |

|

ZP |

ASL a8 |

06 a8 |

2 |

|||

|

ZP, X |

ASL a8, X |

16 a8 |

2 |

|||

|

ABS |

ASL a16 |

0E a16l a16h |

3 |

|||

|

ABS, X |

ASL a16, X |

1E a16l a16h |

3 |

|||

|

BCC |

Переход, если флаг C = 0 |

REL |

BCC i8 |

90 18 |

2 |

|

|

BCS |

Переход, если флаг C = 1 |

REL |

BCS 18 |

B0 18 |

2 |

|

|

BEQ |

Переход, если флаг Z = 1 |

REL |

BEQ 18 |

F018 |

2 |

|

|

BIT |

Установка флагов в соответствии с результатом выполнения поразрядного логического И над содержимым аккумулятора и операнда. Бит 6 результата копируется во флаг V, а бит 7 - во флаг N |

ZP |

BIT a8 |

24 a8 |

2 |

N, V, Z |

|

ABS |

BIT a16 |

|

3 |

|||

|

BMI |

Переход, если флаг N = 1 |

REL |

BMI 18 |

3018 |

2 |

|

|

BNE |

Переход, если флаг Z = 0 |

REL |

BNE 18 |

D0 18 |

2 |

|

|

BPL |

Переход, если флаг N = 0 |

REL |

BPL 18 |

1018 |

2 |

|

|

BRK |

Программное прерывание |

IMPL |

BRK |

00 |

1 |

I |

|

BVC |

Переход, если флаг V = 0 |

REL |

BVC 18 |

5018 |

2 |

|

|

BVS |

Переход, если флаг V = 1 |

REL |

BVS 18 |

7018 |

2 |

|

|

CLC |

Сброс флага C |

IMPL |

CLC |

18 |

1 |

С |

|

CLD |

Сброс флага D |

IMPL |

CLD |

D8 |

1 |

D |

|

CLI |

Сброс флага I (разрешение прерываний) |

IMPL |

CLI |

58 |

1 |

I |

|

CLV |

Сброс флага V |

IMPL |

CLV |

B8 |

1 |

V |

|

CMP |

Установка флагов в соответствии с результатом вычитания операнда из содержимого аккумулятора |

IMM |

CMP #d8 |

C9 d8 |

2 |

N, Z, C |

|

ZP |

CMP a8 |

C5 a8 |

2 |

|||

|

ZP, X |

CMP a8, X |

D5 a8 |

2 |

|||

|

ABS |

CMP a16 |

CD a16l a16h |

3 |

|||

|

ABS, X |

CMP a16, X |

DD a16l a16h |

3 |

|||

|

ABS, Y |

CMP a16, Y |

D9 a16l a16h |

3 |

|||

|

IND, X |

CMP (a8, X) |

C1 a8 |

2 |

|||

|

IND, Y |

CMP (a8), Y |

D1 a8 |

2 |

|||

|

CPX |

Установка флагов в соответствии с результатом вычитания операнда из содержимого регистра X |

IMM |

CPX #d8 |

E0 d8 |

2 |

N, Z, C |

|

ZP |

CPX a8 |

E4d8 |

2 |

|||

|

ABS |

CPX a16 |

EC a16l a16h |

3 |

|||

|

CPY |

Установка флагов в соответствии с результатом вычитания операнда из содержимого аккумулятора |

IMM |

CPY #d8 |

C0 d8 |

2 |

N, Z, C |

|

ZP |

CPY a8 |

C4 a8 |

2 |

|||

|

ABS |

CPY a16 |

CC a16l a16h |

3 |

|||

|

DEC |

Уменьшение операнда на 1 |

ZP |

DEC a8 |

C6 a8 |

2 |

N, Z |

|

ZP, X |

DEC a8, X |

D6 a8 |

2 |

|||

|

ABS |

DEC а16 |

CE a16l a16h |

3 |

|||

|

ABS, X |

DEC a16, X |

DE a16l a16h |

||||

|

DEX |

Х = Х-1 |

IMPL |

DEX |

CA |

1 |

N, Z |

|

DEY |

Y = Y-1 |

IMPL |

DEY |

88 |

1 |

N, Z |

|

EOR |

Поразрядное Исключающее ИЛИ содержимого аккумулятора и операнда |

IMM |

EOR #d8 |

49 d8 |

2 |

N, Z |

|

ZP |

EOR a8 |

45 a8 |

2 |

|||

|

ZP, X |

EOR a8, X |

55 a8 |

2 |

|||

|

ABS |

EOR a16 |

4D a16l a16h |

3 |

|||

|

ABS, X |

EOR a16, X |

5D a16l a16h |

3 |

|||

|

ABS, Y |

EOR a16, Y |

59 a16l a16h |

3 |

|||

|

IND, X |

EOR (a8, X) |

41 a8 |

2 |

|||

|

IND, Y |

EOR (a8), Y |

51 a8 |

2 |

|||

|

INC |

Увеличение операнда на 1 |

ZP |

INC a8 |

E6 a8 |

2 |

N, Z |

|

ZP, X |

INC a8, X |

F6 a8 |

2 |

|||

|

ABS |

INC a16 |

EE a16l a16h |

3 |

|||

|

ABS, X |

INC a16, X |

FE a16l a16h |

3 |

|||

|

INX |

Х = X+1 |

IMPL |

INX |

E8 |

1 |

N, Z |

|

INY |

Y = Y+1 |

IMPL |

INY |

C8 |

1 |

N, Z |

|

JMP |

Переход по указанному адресу |

ABS |

JMP a16 |

|

2 |

|

|

IND |

JMP (a 16) |

|

2 |

|||

|

JSR |

Вызов подпрограммы с указанным адресом. В стеке сохраняется только адрес возврата |

ABS |

JSR a16 |

20 a16l a16h |

3 |

|

|

LDA |

Загрузка операнда в аккумулятор |

IMM |

LDA #d8 |

A9d8 |

2 |

N, Z |

|

ZP |

LDA a8 |

A5a8 |

2 |

|||

|

ZP, X |

LDA a8, X |

B5a8 |

2 |

|||

|

ABS |

LDA a16 |

AD a16l a16h |

3 |

|||

|

ABS, X |

LDA a16, X |

BD a16l a16h |

3 |

|||

|

ABS, Y |

LDA a16, Y |

B9 a16l a16h |

3 |

|||

|

IND, X |

LDA (a8, X) |

A1 a8 |

2 |

|||

|

IND, Y |

LDA (a8), Y |

B1 a8 |

2 |

|||

|

LDX |

Загрузка операнда в регистр X |

IMM |

LDX #d8 |

A2 d8 |

2 |

H, Z |

|

ZP |

LDX a8 |

A6a8 |

2 |

|||

|

ZP, Y |

LDX a8, Y |

B6a8 |

2 |

|||

|

ABS |

LDX a16 |

AE a16l a16h |

3 |

|||

|

ABS, Y |

LDX a16, Y |

BE a16l a16h |

3 |

|||

|

LDY |

Загрузка операнда в регистр Y |

IMM |

LDY #d8 |

A0 d8 |

2 |

N, Z |

|

ZP |

LDY a8 |

A4 a8 |

2 |

|||

|

ZP, Y |

LDY a8, Y |

B4 a8 |

2 |

|||

|

ABS |

LDY a16 |

AC a16l a16h |

3 |

|||

|

ABS, Y |

LDY a16, Y |

BC a16l a16h |

3 |

|||

|

LSR |

Логический сдвиг операнда вправо (деление на 2) |

ACC |

LSR A |

4A |

1 |

N, Z, C |

|

ZP |

LSR a8 |

46 a8 |

2 |

|||

|

ZP, X |

LSR a8, X |

56 a8 |

2 |

|||

|

ABS |

LSR a16 |

4E a16l a16h |

3 |

|||

|

ABS, X |

LSR a16, X |

5E a16l a16h |

3 |

|||

|

NOP |

Нет операции |

IMPL |

NOP |

EA |

1 |

|

|

ORA |

Поразрядное логическое ИЛИ содержимого аккумулятора и операнда |

IMM |

ORA #d8 |

09 d8 |

2 |

N, Z |

|

ZP |

ORA a8 |

05 a8 |

2 |

|||

|

ZP, X |

ORA a8, X |

15 a8 |

2 |

|||

|

ABS |

ORA a16 |

0D a16l a16h |

3 |

|||

|

ABS, X |

ORA a16, X |

1D a16l a16h |

3 |

|||

|

ABS, Y |

ORA a16, Y |

19 a16l a16h |

3 |

|||

|

IND, X |

ORA (a8, X) |

01 a8 |

2 |

|||

|

IND, Y |

ORA (a8), Y |

11 a8 |

2 |

|||

|

PHA |

Помещение содержимого аккумулятора в стек |

IMPL |

PHA |

48 |

1 |

|

|

PHP |

Помещение регистра состояния в стек |

IMPL |

PHP |

08 |

1 |

|

|

PLA |

Помещение байта с вершины стека в аккумулятор |

IMPL |

PLA |

68 |

1 |

|

|

PLP |

Помещение байта с вершины стека в регистр состояния |

IMPL |

PLP |

28 |

1 |

Все флаги |

|

ROL |

Циклический сдвиг операнда влево |

АСС |

ROL A |

2A |

1 |

N, Z, C |

|

ZP |

ROL a8 |

26 a8 |

2 |

|||

|

ZP, X |

ROL a8, X |

36 a8 |

2 |

|||

|

ABS |

ROL a16 |

2E a16l a16h |

3 |

|||

|

ABS, X |

ROL a16, X |

3E a16l a16h |

3 |

|||

|

ROR |

Циклический сдвиг операнда вправо |

АСС |

ROR A |

6A |

1 |

N, Z, C |

|

ZP |

ROR a8 |

66 a8 |

2 |

|||

|

ZP, X |

ROR a8, X |

76 a8 |

2 |

|||

|

ABS |

ROR a16 |

6E a16l a16h |

3 |

|||

|

ABS, X |

ROR a16, X |

7E a16l a16h |

3 |

|||

|

RTI |

Возврат из прерывания |

IMPL |

RTI |

40 |

1 |

Все флаги |

|

RTS |

Возврат из подпрограммы |

IMPL |

RTS |

60 |

1 |

|

|

SBC |

Вычитание операнда из содержимого аккумулятора с учетом флага переноса |

IMM |

SBC #d8 |

E9 d8 |

2 |

N, V, Z, C |

|

ZP |

SBC a8 |

E5 a8 |

2 |

|||

|

ZP, X |

SBC a8, X |

F5 a8 |

2 |

|||

|

ABS |

SBC a16 |

ED a16l a16h |

3 |

|||

|

ABS, X |

SBC a16, X |

FD a16l a16h |

3 |

|||

|

ABS, Y |

SBC a16, Y |

F9 a16l a16h |

3 |

|||

|

IND, X |

SBC (a8, X) |

E1 a8 |

2 |

|||

|

IND, Y |

SBC (a8), Y |

F1 a8 |

2 |

|||

|

SEC |

Установка флага C |

IMPL |

SEC |

38 |

1 |

С |

|

SED |

Установка флага D |

IMPL |

SED |

F8 |

1 |

D |

|

SEI |

Установка флага I (запрещение прерываний) |

IMPL |

SEI |

78 |

1 |

I |

|

STA |

Запись содержимого аккумулятора в память |

ZP |

STA a8 |

85 a8 |

2 |

|

|

ZP, X |

STA a8, X |

95 a8 |

2 |

|||

|

ABS |

STA a16 |

8D a16l a16h |

3 |

|||

|

ABS, X |

STA a16, X |

9D a16l a16h |

3 |

|||

|

ABS, Y |

STA a16; Y |

99 a16l a16h |

3 |

|||

|

IND, X |

STA (a8, X) |

81 a8 |

2 |

|||

|

IND, Y |

STA (a8) |

91 a8 |

2 |

|||

|

STX |

Запись содержимого регистра X в память |

ZP |

STX a8 |

86 a8 |

2 |

|

|

ZP, Y |

STX a8, Y |

96 a8 |

2 |

|||

|

ABS |

STX a16 |

8E a16l a16h |

3 |

|||

|

STY |

Запись содержимого регистра Y в память |

ZP |

STY a8 |

84 a8 |

2 |

|

|

ZP, X |

STY a8, X |

94 a8 |

2 |

|||

|

ABS |

STY a16 |

|

3 |

|||

|

TAX |

Пересылка содержимого аккумулятора в регистр X |

IMPL |

TAX |

AA |

1 |

N, Z |

|

|

Пересылка содержимого аккумулятора в регистр Y |

IMPL |

TAY |

A8 |

1 |

N, Z |

|

TSX |

Пересылка содержимого указателя стека в регистр X |

IMPL |

TSX |

BA |

1 |

N, Z |

|

TXA |

Пересылка содержимого регистра X в аккумулятор |

IMPL |

TXA |

8A |

1 |

N, Z |

|

TXS |

Пересылка содержимого регистра X в указатель стека |

IMPL |

TXS |

9A |

1 |

|

|

TYA |

Пересылка содержимого регистра Y в аккумулятор |

IMPL |

TYA |

98 |

1 |

N, Z |

Условные обозначения:

а16 - 16-разрядный адрес

a16h - старший байт 16-разрядного адреса

а16l - младший байт 16-разрядного адреса

а8 - 8-разрядный адрес в нулевой странице

d8 - непосредственный 8-разрядный операнд

i8 - 8-разрядное смещение в диапазоне от -128 до 127

Также приведем матрицу системы команд (красным цветом отмечены недокументированные инструкции – в базовой архитектуре 6502 они отсутствуют, но контроллером 6561, вероятно, поддерживаются).

|

76543210 |

xxx000xx |

xxx010xx |

xxx100xx |

xxx110xx |

xxx001xx |

xxx011xx |

xxx101xx |

xxx111xx |

|

000xxx00 |

BRK IMM |

PHP |

BPL REL |

CLC |

DOP ZP |

TOP ABS |

DOP ZPX |

TOP ABX |

|

001xxx00 |

JSR ABS |

PLP |

BMI REL |

SEC |

BIT ZP |

BIT ABS |

DOP ZPX |

TOP ABX |

|

010xxx00 |

RTI |

PHA |

BVC REL |

CLI |

DOP ZP |

JMP ABS |

DOP ZPX |

TOP ABX |

|

011xxx00 |

RTS |

PLA |

BVS REL |

SEI |

DOP ZP |

JMP |

DOP ZPX |

TOP ABX |

|

100xxx00 |

DOP IMM |

DEY |

BCC REL |

TYA |

STY ZP |

STY ABS |

STY ZPX |

SYA ABX |

|

101xxx00 |

LDY IMM |

TAY |

BCS REL |

CLV |

LDY ZP |

LDY ABS |

LDY ZPX |

LDY ABX |

|

110xxx00 |

CPY IMM |

INY |

BNE REL |

CLD |

CPY ZP |

CPY ABS |

DOP ZPX |

TOP ABX |

|

111xxx00 |

CPX IMM |

INX |

BEQ REL |

SED |

CPX ZP |

CPX ABS |

DOP ZPX |

TOP ABX |

|

000xxx01 |

ORA NDX |

ORA IMM |

ORA NDY |

ORA ABY |

ORA ZP |

ORA ABS |

ORA ZPX |

ORA ABX |

|

001xxx01 |

AND NDX |

AND IMM |

AND NDY |

AND ABY |

AND ZP |

AND ABS |

AND ZPX |

AND ABX |

|

010xxx01 |

EOR NDX |

EOR IMM |

EOR NDY |

EOR ABY |

EOR ZP |

EOR ABS |

EOR ZPX |

EOR ABX |

|

011xxx01 |

ADC NDX |

ADC IMM |

ADC NDY |

ADC ABY |

ADC ZP |

ADC ABS |

ADC ZPX |

ADC ABX |

|

100xxx01 |

STA NDX |

DOP IMM |

STA NDY |

STA ABY |

STA ZP |

STA ABS |

STA ZPX |

STA ABX |

|

101xxx01 |

LDA NDX |

LDA IMM |

LDA NDY |

LDA ABY |

LDA ZP |

LDA ABS |

LDA ZPX |

LDA ABX |

|

110xxx01 |

CMP NDX |

CMP IMM |

CMP NDY |

CMP ABY |

CMP ZP |

CMP ABS |

CMP ZPX |

CMP ABX |

|

111xxx01 |

SBC NDX |

SBC IMM |

SBC NDY |

SBC ABY |

SBC ZP |

SBC ABS |

SBC ZPX |

SBC ABX |

|

000xxx10 |

KIL |

ASL A |

KIL |

NOP |

ASL ZP |

ASL ABS |

ASL ZPX |

ASL ABX |

|

001xxx10 |

KIL |

ROL A |

KIL |

NOP |

ROL ZP |

ROL ABS |

ROL ZPX |

ROL ABX |

|

010xxx10 |

KIL |

LSR A |

KIL |

NOP |

LSR ZP |

LSR ABS |

LSR ZPX |

LSR ABX |

|

011xxx10 |

KIL |

ROR A |

KIL |

NOP |

ROR ZP |

ROR ABS |

ROR ZPX |

ROR ABX |

|

100xxx10 |

DOP IMM |

TXA |

KIL |

TXS |

STX ZP |

STX ABS |

STX ZPY |

SXA ABY |

|

101xxx10 |

LDX IMM |

TAX |

KIL |

TSX |

LDX ZP |

LDX ABS |

LDX ZPY |

LDX ABY |

|

110xxx10 |

DOP IMM |

DEX |

KIL |

NOP |

DEC ZP |

DEC ABS |

DEC ZPX |

DEC ABX |

|

111xxx10 |

DOP IMM |

NOP |

KIL |

NOP |

INC ZP |

INC ABS |

INC ZPX |

INC ABX |

|

000xxx11 |

SLO NDX |

AAC IMM |

SLO NDY |

SLO ABY |

SLO ZP |

SLO ABS |

SLO ZPX |

SLO ABX |

|

001xxx11 |

RLA NDX |

AAC IMM |

RLA NDY |

RLA ABY |

RLA ZP |

RLA ABS |

RLA ZPX |

RLA ABX |

|

010xxx11 |

SRE NDX |

ASR IMM |

SRE NDY |

SRE ABY |

SRE ZP |

SRE ABS |

SRE ZPX |

SRE ABX |

|

011xxx11 |

RRA NDX |

ARR IMM |

RRA NDY |

RRA ABY |

RRA ZP |

RRA ABS |

RRA ZPX |

RRA ABX |

|

100xxx11 |

AAX NDX |

XAA IMM |

AXA NDY |

XAS ABY |

AAX ZP |

AAX ABS |

AAX ZPY |

AXA ABY |

|

101xxx11 |

LAX NDX |

ATX IMM |

LAX NDY |

LAR ABY |

LAX ZP |

LAX ABS |

LAX ZPY |

LAX ABY |

|

110xxx11 |

DCP NDX |

AXS IMM |

DCP NDY |

DCP ABY |

DCP ZP |

DCP ABS |

DCP ZPX |

DCP ABX |

|

111xxx11 |

ISC NDX |

SBC IMM |

ISC NDY |

ISC ABY |

ISC ZP |

ISC ABS |

ISC ZPX |

ISC ABX |

Источник - тут

6502 Instruction Set

| HI | LO-NIBBLE | |||||||||||||||

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | |

| 00 | BRK impl | ORA X,ind | ??? --- | ??? --- | ??? --- | ORA zpg | ASL zpg | ??? --- | PHP impl | ORA # | ASL A | ??? --- | ??? --- | ORA abs | ASL abs | ??? --- |

| 10 | BPL rel | ORA ind,Y | ??? --- | ??? --- | ??? --- | ORA zpg,X | ASL zpg,X | ??? --- | CLC impl | ORA abs,Y | ??? --- | ??? --- | ??? --- | ORA abs,X | ASL abs,X | ??? --- |

| 20 | JSR abs | AND X,ind | ??? --- | ??? --- | BIT zpg | AND zpg | ROL zpg | ??? --- | PLP impl | AND # | ROL A | ??? --- | BIT abs | AND abs | ROL abs | ??? --- |

| 30 | BMI rel | AND ind,Y | ??? --- | ??? --- | ??? --- | AND zpg,X | ROL zpg,X | ??? --- | SEC impl | AND abs,Y | ??? --- | ??? --- | ??? --- | AND abs,X | ROL abs,X | ??? --- |

| 40 | RTI impl | EOR X,ind | ??? --- | ??? --- | ??? --- | EOR zpg | LSR zpg | ??? --- | PHA impl | EOR # | LSR A | ??? --- | JMP abs | EOR abs | LSR abs | ??? --- |

| 50 | BVC rel | EOR ind,Y | ??? --- | ??? --- | ??? --- | EOR zpg,X | LSR zpg,X | ??? --- | CLI impl | EOR abs,Y | ??? --- | ??? --- | ??? --- | EOR abs,X | LSR abs,X | ??? --- |

| 60 | RTS impl | ADC X,ind | ??? --- | ??? --- | ??? --- | ADC zpg | ROR zpg | ??? --- | PLA impl | ADC # | ROR A | ??? --- | JMP ind | ADC abs | ROR abs | ??? --- |

| 70 | BVS rel | ADC ind,Y | ??? --- | ??? --- | ??? --- | ADC zpg,X | ROR zpg,X | ??? --- | SEI impl | ADC abs,Y | ??? --- | ??? --- | ??? --- | ADC abs,X | ROR abs,X | ??? --- |

| 80 | ??? --- | STA X,ind | ??? --- | ??? --- | STY zpg | STA zpg | STX zpg | ??? --- | DEY impl | ??? --- | TXA impl | ??? --- | STY abs | STA abs | STX abs | ??? --- |

| 90 | BCC rel | STA ind,Y | ??? --- | ??? --- | STY zpg,X | STA zpg,X | STX zpg,Y | ??? --- | TYA impl | STA abs,Y | TXS impl | ??? --- | ??? --- | STA abs,X | ??? --- | ??? --- |

| A0 | LDY # | LDA X,ind | LDX # | ??? --- | LDY zpg | LDA zpg | LDX zpg | ??? --- | TAY impl | LDA # | TAX impl | ??? --- | LDY abs | LDA abs | LDX abs | ??? --- |

| B0 | BCS rel | LDA ind,Y | ??? --- | ??? --- | LDY zpg,X | LDA zpg,X | LDX zpg,Y | ??? --- | CLV impl | LDA abs,Y | TSX impl | ??? --- | LDY abs,X | LDA abs,X | LDX abs,Y | ??? --- |

| C0 | CPY # | CMP X,ind | ??? --- | ??? --- | CPY zpg | CMP zpg | DEC zpg | ??? --- | INY impl | CMP # | DEX impl | ??? --- | CPY abs | CMP abs | DEC abs | ??? --- |

| D0 | BNE rel | CMP ind,Y | ??? --- | ??? --- | ??? --- | CMP zpg,X | DEC zpg,X | ??? --- | CLD impl | CMP abs,Y | ??? --- | ??? --- | ??? --- | CMP abs,X | DEC abs,X | ??? --- |

| E0 | CPX # | SBC X,ind | ??? --- | ??? --- | CPX zpg | SBC zpg | INC zpg | ??? --- | INX impl | SBC # | NOP impl | ??? --- | CPX abs | SBC abs | INC abs | ??? --- |

| F0 | BEQ rel | SBC ind,Y | ??? --- | ??? --- | ??? --- | SBC zpg,X | INC zpg,X | ??? --- | SED impl | SBC abs,Y | ??? --- | ??? --- | ??? --- | SBC abs,X | INC abs,X | ??? --- |

Address Modes:

| A | .... | Accumulator | OPC A | operand is AC | |||

| abs | .... | absolute | OPC $HHLL | operand is address $HHLL | |||

| abs,X | .... | absolute, X-indexed | OPC $HHLL,X | operand is address incremented by X with carry | |||

| abs,Y | .... | absolute, Y-indexed | OPC $HHLL,Y | operand is address incremented by Y with carry | |||

| # | .... | immediate | OPC #$BB | operand is byte (BB) | |||

| impl | .... | implied | OPC | operand implied | |||

| ind | .... | indirect | OPC ($HHLL) | operand is effective address; effective address is value of address | |||

| X,ind | .... | X-indexed, indirect | OPC ($BB,X) | operand is effective zeropage address; effective address is byte (BB) incremented by X without carry | |||

| ind,Y | .... | indirect, Y-indexed | OPC ($LL),Y | operand is effective address incremented by Y with carry; effective address is word at zeropage address | |||

| rel | .... | relative | OPC $BB | branch target is PC + offset (BB), bit 7 signifies negative offset | |||

| zpg | .... | zeropage | OPC $LL | operand is of address; address hibyte = zero ($00xx) | |||

| zpg,X | .... | zeropage, X-indexed | OPC $LL,X | operand is address incremented by X; address hibyte = zero ($00xx); no page transition | |||

| zpg,Y | .... | zeropage, Y-indexed | OPC $LL,Y | operand is address incremented by Y; address hibyte = zero ($00xx); no page transition |

Instructions by Name:

| ADC | .... | add with carry |

| AND | .... | and (with accumulator) |

| ASL | .... | arithmetic shift left |

| BCC | .... | branch on carry clear |

| BCS | .... | branch on carry set |

| BEQ | .... | branch on equal (zero set) |

| BIT | .... | bit test |

| BMI | .... | branch on minus (negative set) |

| BNE | .... | branch on not equal (zero clear) |

| BPL | .... | branch on plus (negative clear) |

| BRK | .... | interrupt |

| BVC | .... | branch on overflow clear |

| BVS | .... | branch on overflow set |

| CLC | .... | clear carry |

| CLD | .... | clear decimal |

| CLI | .... | clear interrupt disable |

| CLV | .... | clear overflow |

| CMP | .... | compare (with accumulator) |

| CPX | .... | compare with X |

| CPY | .... | compare with Y |

| DEC | .... | decrement |

| DEX | .... | decrement X |

| DEY | .... | decrement Y |

| EOR | .... | exclusive or (with accumulator) |

| INC | .... | increment |

| INX | .... | increment X |

| INY | .... | increment Y |

| JMP | .... | jump |

| JSR | .... | jump subroutine |

| LDA | .... | load accumulator |

| LDY | .... | load X |

| LDY | .... | load Y |

| LSR | .... | logical shift right |

| NOP | .... | no operation |

| ORA | .... | or with accumulator |

| PHA | .... | push accumulator |

| PHP | .... | push processor status (SR) |

| PLA | .... | pull accumulator |

| PLP | .... | pull processor status (SR) |

| ROL | .... | rotate left |

| ROR | .... | rotate right |

| RTI | .... | return from interrupt |

| RTS | .... | return from subroutine |

| SBC | .... | subtract with carry |

| SEC | .... | set carry |

| SED | .... | set decimal |

| SEI | .... | set interrupt disable |

| STA | .... | store accumulator |

| STX | .... | store X |

| STY | .... | store Y |

| TAX | .... | transfer accumulator to X |

| TAY | .... | transfer accumulator to Y |

| TSX | .... | transfer stack pointer to X |

| TXA | .... | transfer X to accumulator |

| TXS | .... | transfer X to stack pointer |

| TYA | .... | transfer Y to accumulator |

Registers:

| PC | .... | program counter | (16 bit) |

| AC | .... | accumulator | (8 bit) |

| X | .... | X register | (8 bit) |

| Y | .... | Y register | (8 bit) |

| SR | .... | status register [NV-BDIZC] | (8 bit) |

| SP | .... | stack pointer | (8 bit) |

SR Flags (bit 7 to bit 0):

| N | .... | Negative |

| V | .... | Overflow |

| - | .... | ignored |

| B | .... | Break |

| D | .... | Decimal (use BCD for arithmetics) |

| I | .... | Interrupt (IRQ disable) |

| Z | .... | Zero |

| C | .... | Carry |

Processor Stack:

LIFO, top down, 8 bit range, 0x0100 - 0x01FF

Bytes, Words, Addressing:

8 bit bytes, 16 bit words in lobyte-hibyte representation (Little-Endian).

16 bit address range, operands follow instruction codes.

Vendor:

MOS Technology, 1975

APPENDIX A: 6502 Instructions in Detail

ADC Add Memory to Accumulator with Carry

A + M + C -> A, C N Z C I D V

+ + + - - +

addressing assembler opc bytes cyles

--------------------------------------------

immidiate ADC #oper 69 2 2

zeropage ADC oper 65 2 3

zeropage,X ADC oper,X 75 2 4

absolute ADC oper 6D 3 4

absolute,X ADC oper,X 7D 3 4*

absolute,Y ADC oper,Y 79 3 4*

(indirect,X) ADC (oper,X) 61 2 6

(indirect),Y ADC (oper),Y 71 2 5*

AND AND Memory with Accumulator

A AND M -> A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate AND #oper 29 2 2

zeropage AND oper 25 2 3

zeropage,X AND oper,X 35 2 4

absolute AND oper 2D 3 4

absolute,X AND oper,X 3D 3 4*

absolute,Y AND oper,Y 39 3 4*

(indirect,X) AND (oper,X) 21 2 6

(indirect),Y AND (oper),Y 31 2 5*

ASL Shift Left One Bit (Memory or Accumulator)

C <- [76543210] <- 0 N Z C I D V

+ + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

accumulator ASL A 0A 1 2

zeropage ASL oper 06 2 5

zeropage,X ASL oper,X 16 2 6

absolute ASL oper 0E 3 6

absolute,X ASL oper,X 1E 3 7

BCC Branch on Carry Clear

branch on C = 0 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BCC oper 90 2 2**

BCS Branch on Carry Set

branch on C = 1 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BCS oper B0 2 2**

BEQ Branch on Result Zero

branch on Z = 1 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BEQ oper F0 2 2**

BIT Test Bits in Memory with Accumulator

bits 7 and 6 of operand are transfered to bit 7 and 6 of SR (N,V);

the zeroflag is set to the result of operand AND accumulator.

A AND M, M7 -> N, M6 -> V N Z C I D V

M7 + - - - M6

addressing assembler opc bytes cyles

--------------------------------------------

zeropage BIT oper 24 2 3

absolute BIT oper 2C 3 4

BMI Branch on Result Minus

branch on N = 1 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BMI oper 30 2 2**

BNE Branch on Result not Zero

branch on Z = 0 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BNE oper D0 2 2**

BPL Branch on Result Plus

branch on N = 0 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BPL oper 10 2 2**

BRK Force Break

interrupt, N Z C I D V

push PC+2, push SR - - - 1 - -

addressing assembler opc bytes cyles

--------------------------------------------

implied BRK 00 1 7

BVC Branch on Overflow Clear

branch on V = 0 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BVC oper 50 2 2**

BVS Branch on Overflow Set

branch on V = 1 N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

relative BVC oper 70 2 2**

CLC Clear Carry Flag

0 -> C N Z C I D V

- - 0 - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied CLC 18 1 2

CLD Clear Decimal Mode

0 -> D N Z C I D V

- - - - 0 -

addressing assembler opc bytes cyles

--------------------------------------------

implied CLD D8 1 2

CLI Clear Interrupt Disable Bit

0 -> I N Z C I D V

- - - 0 - -

addressing assembler opc bytes cyles

--------------------------------------------

implied CLI 58 1 2

CLV Clear Overflow Flag

0 -> V N Z C I D V

- - - - - 0

addressing assembler opc bytes cyles

--------------------------------------------

implied CLV B8 1 2

CMP Compare Memory with Accumulator

A - M N Z C I D V

+ + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate CMP #oper C9 2 2

zeropage CMP oper C5 2 3

zeropage,X CMP oper,X D5 2 4

absolute CMP oper CD 3 4

absolute,X CMP oper,X DD 3 4*

absolute,Y CMP oper,Y D9 3 4*

(indirect,X) CMP (oper,X) C1 2 6

(indirect),Y CMP (oper),Y D1 2 5*

CPX Compare Memory and Index X

X - M N Z C I D V

+ + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate CPX #oper E0 2 2

zeropage CPX oper E4 2 3

absolute CPX oper EC 3 4

CPY Compare Memory and Index Y

Y - M N Z C I D V

+ + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate CPY #oper C0 2 2

zeropage CPY oper C4 2 3

absolute CPY oper CC 3 4

DEC Decrement Memory by One

M - 1 -> M N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

zeropage DEC oper C6 2 5

zeropage,X DEC oper,X D6 2 6

absolute DEC oper CE 3 3

absolute,X DEC oper,X DE 3 7

DEX Decrement Index X by One

X - 1 -> X N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied DEC CA 1 2

DEY Decrement Index Y by One

Y - 1 -> Y N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied DEC 88 1 2

EOR Exclusive-OR Memory with Accumulator

A EOR M -> A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate EOR #oper 49 2 2

zeropage EOR oper 45 2 3

zeropage,X EOR oper,X 55 2 4

absolute EOR oper 4D 3 4

absolute,X EOR oper,X 5D 3 4*

absolute,Y EOR oper,Y 59 3 4*

(indirect,X) EOR (oper,X) 41 2 6

(indirect),Y EOR (oper),Y 51 2 5*

INC Increment Memory by One

M + 1 -> M N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

zeropage INC oper E6 2 5

zeropage,X INC oper,X F6 2 6

absolute INC oper EE 3 6

absolute,X INC oper,X FE 3 7

INX Increment Index X by One

X + 1 -> X N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied INX E8 1 2

INY Increment Index Y by One

Y + 1 -> Y N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied INY C8 1 2

JMP Jump to New Location

(PC+1) -> PCL N Z C I D V

(PC+2) -> PCH - - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

absolute JMP oper 4C 3 3

indirect JMP (oper) 6C 3 5

JSR Jump to New Location Saving Return Address

push (PC+2), N Z C I D V

(PC+1) -> PCL - - - - - -

(PC+2) -> PCH

addressing assembler opc bytes cyles

--------------------------------------------

absolute JSR oper 20 3 6

LDA Load Accumulator with Memory

M -> A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate LDA #oper A9 2 2

zeropage LDA oper A5 2 3

zeropage,X LDA oper,X B5 2 4

absolute LDA oper AD 3 4

absolute,X LDA oper,X BD 3 4*

absolute,Y LDA oper,Y B9 3 4*

(indirect,X) LDA (oper,X) A1 2 6

(indirect),Y LDA (oper),Y B1 2 5*

LDX Load Index X with Memory

M -> X N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate LDX #oper A2 2 2

zeropage LDX oper A6 2 3

zeropage,Y LDX oper,Y B6 2 4

absolute LDX oper AE 3 4

absolute,Y LDX oper,Y BE 3 4*

LDY Load Index Y with Memory

M -> Y N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate LDY #oper A0 2 2

zeropage LDY oper A4 2 3

zeropage,X LDY oper,X B4 2 4

absolute LDY oper AC 3 4

absolute,X LDY oper,X BC 3 4*

LSR Shift One Bit Right (Memory or Accumulator)

0 -> [76543210] -> C N Z C I D V

- + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

accumulator LSR A 4A 1 2

zeropage LSR oper 46 2 5

zeropage,X LSR oper,X 56 2 6

absolute LSR oper 4E 3 6

absolute,X LSR oper,X 5E 3 7

NOP No Operation

--- N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied NOP EA 1 2

ORA OR Memory with Accumulator

A OR M -> A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

immidiate ORA #oper 09 2 2

zeropage ORA oper 05 2 3

zeropage,X ORA oper,X 15 2 4

absolute ORA oper 0D 3 4

absolute,X ORA oper,X 1D 3 4*

absolute,Y ORA oper,Y 19 3 4*

(indirect,X) ORA (oper,X) 01 2 6

(indirect),Y ORA (oper),Y 11 2 5*

PHA Push Accumulator on Stack

push A N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied PHA 48 1 3

PHP Push Processor Status on Stack

push SR N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied PHP 08 1 3

PLA Pull Accumulator from Stack

pull A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied PLA 68 1 4

PLP Pull Processor Status from Stack

pull SR N Z C I D V

from stack

addressing assembler opc bytes cyles

--------------------------------------------

implied PHP 28 1 4

ROL Rotate One Bit Left (Memory or Accumulator)

C <- [76543210] <- C N Z C I D V

+ + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

accumulator ROL A 2A 1 2

zeropage ROL oper 26 2 5

zeropage,X ROL oper,X 36 2 6

absolute ROL oper 2E 3 6

absolute,X ROL oper,X 3E 3 7

ROR Rotate One Bit Right (Memory or Accumulator)

C -> [76543210] -> C N Z C I D V

+ + + - - -

addressing assembler opc bytes cyles

--------------------------------------------

accumulator ROR A 6A 1 2

zeropage ROR oper 66 2 5

zeropage,X ROR oper,X 76 2 6

absolute ROR oper 6E 3 6

absolute,X ROR oper,X 7E 3 7

RTI Return from Interrupt

pull SR, pull PC N Z C I D V

from stack

addressing assembler opc bytes cyles

--------------------------------------------

implied RTI 40 1 6

RTS Return from Subroutine

pull PC, PC+1 -> PC N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied RTS 60 1 6

SBC Subtract Memory from Accumulator with Borrow

A - M - C -> A N Z C I D V

+ + + - - +

addressing assembler opc bytes cyles

--------------------------------------------

immidiate SBC #oper E9 2 2

zeropage SBC oper E5 2 3

zeropage,X SBC oper,X F5 2 4

absolute SBC oper ED 3 4

absolute,X SBC oper,X FD 3 4*

absolute,Y SBC oper,Y F9 3 4*

(indirect,X) SBC (oper,X) E1 2 6

(indirect),Y SBC (oper),Y F1 2 5*

SEC Set Carry Flag

1 -> C N Z C I D V

- - 1 - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied SEC 38 1 2

SED Set Decimal Flag

1 -> D N Z C I D V

- - - - 1 -

addressing assembler opc bytes cyles

--------------------------------------------

implied SED F8 1 2

SEI Set Interrupt Disable Status

1 -> I N Z C I D V

- - - 1 - -

addressing assembler opc bytes cyles

--------------------------------------------

implied SEI 78 1 2

STA Store Accumulator in Memory

A -> M N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

zeropage STA oper 85 2 3

zeropage,X STA oper,X 95 2 4

absolute STA oper 8D 3 4

absolute,X STA oper,X 9D 3 5

absolute,Y STA oper,Y 99 3 5

(indirect,X) STA (oper,X) 81 2 6

(indirect),Y STA (oper),Y 91 2 6

STX Store Index X in Memory

X -> M N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

zeropage STX oper 86 2 3

zeropage,Y STX oper,Y 96 2 4

absolute STX oper 8E 3 4

STY Sore Index Y in Memory

Y -> M N Z C I D V

- - - - - -

addressing assembler opc bytes cyles

--------------------------------------------

zeropage STY oper 84 2 3

zeropage,X STY oper,X 94 2 4

absolute STY oper 8C 3 4

TAX Transfer Accumulator to Index X

A -> X N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied TAX AA 1 2

TAY Transfer Accumulator to Index Y

A -> Y N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied TAY A8 1 2

TSX Transfer Stack Pointer to Index X

SP -> X N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied TSX BA 1 2

TXA Transfer Index X to Accumulator

X -> A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied TXA 8A 1 2

TXS Transfer Index X to Stack Register

X -> SP N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied TXS 9A 1 2

TYA Transfer Index Y to Accumulator

Y -> A N Z C I D V

+ + - - - -

addressing assembler opc bytes cyles

--------------------------------------------

implied TYA 98 1 2

* add 1 to cycles if page boundery is crossed

** add 1 to cycles if branch occurs on same page

add 2 to cycles if branch occurs to different page

Legend to Flags: + .... modified

- .... not modified

1 .... set

0 .... cleared

M6 .... memory bit 6

M7 .... memory bit 7

Note on assembler syntax:

Most assemblers employ "OPC *oper" for forced zeropage addressing.

APENDIX B: The 65xx-Family:

Type Features, Comments

-------------------------------------

6502 NMOS, 16 bit address bus, 8 bit data bus

6502A accelerated version of 6502

6502C accelerated version of 6502, CMOS

65C02 16 bit version, additional instructions and address modes

6503, 6505, 6506 12 bit address bus [4 KiB]

6504 13 bit address bus [8 KiB]

6507 13 bit address bus [8 KiB], no interrupts

6509 20 bit address bus [1 MiB] by bankswitching

6510 as 6502 with additional 6 bit I/O-port

6511 integrated micro controler with I/O-port, serial interface, and RAM (Rockwell)

65F11 as 6511, integrated FORTH interpreter

7501 as 6502, HMOS

8500 as 6510, CMOS

8502 as 6510 with switchable 2 MHz option, 7 bit I/O-port

65816 (65C816) 16 bit registers and ALU, 24 bit address bus [16 MiB], up to 24 MHz (Western Design Center)

65802 (65C802) as 65816, pin compatible to 6502, 64 KiB address bus, up to 16 MHz

Disclaimer:

Errors excepted. The information is provided for free and AS IS, therefore without any warranty;

without even the implied warranty of merchantability or fitness for a particular purpose.

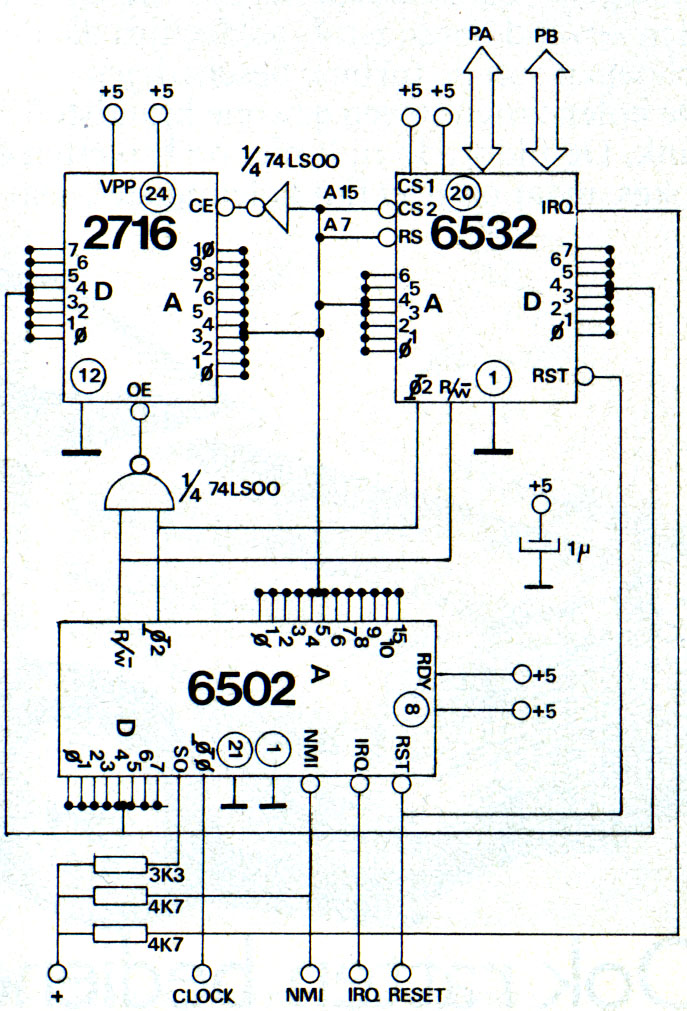

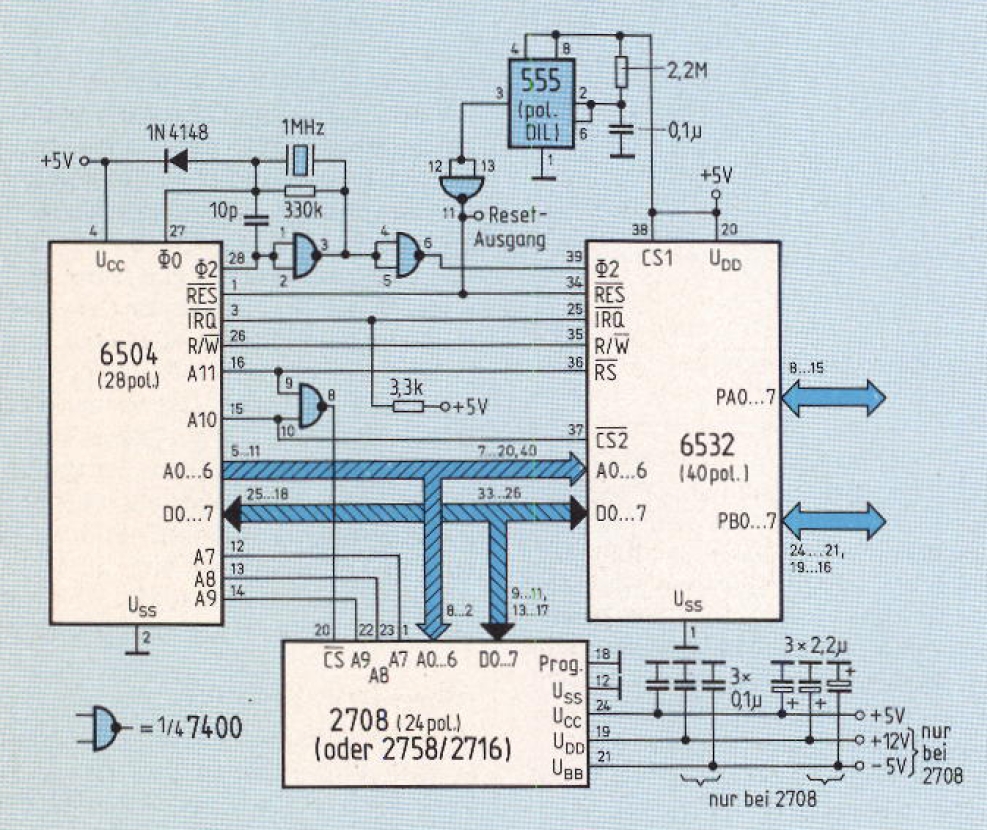

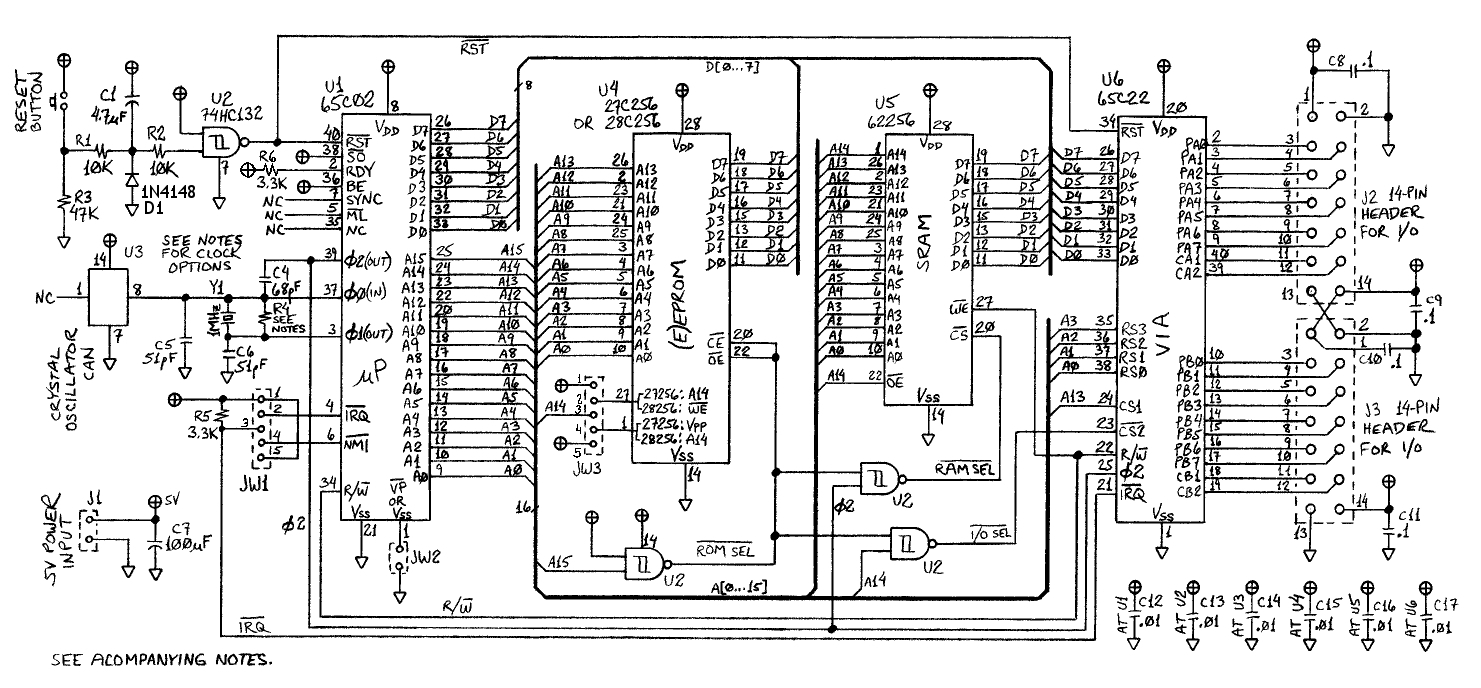

Basic 6502 computer (link)

DIY ("Do-It-Yourself") 6502 computer - link