Архитектура процессора

Регистры:

- R0, R1, R2, R3: Четыре рабочих регистра, каждый размером 8 бит.

- Флаги (F): Регистр флагов размером 8 бит, содержащий информацию о состоянии процессора.

- Счетчик команд (PC): Регистр, который хранит адрес следующей команды для выполнения.

Команды:

Команды регистр-регистр

Эти команды выполняют операции между регистрами:

- ADD Rdest, Rsrc: Сложение значения из регистра Rsrc с Rdest, результат сохраняется в Rdest.

- SUB Rdest, Rsrc: Вычитание значения из Rsrc из Rdest, результат сохраняется в Rdest.

- MUL Rdest, Rsrc: Умножение значения из Rsrc на Rdest, результат сохраняется в Rdest.

- DIV Rdest, Rsrc: Деление значения из Rdest на Rsrc, результат сохраняется в Rdest.

- MOV Rdest, Rsrc: Копирование значения из Rsrc в Rdest.

Команды регистр-память

Эти команды выполняют операции между регистрами и памятью:

- LOAD Rdest, addr: Загрузка 8-битного значения из памяти по адресу addr в регистр Rdest.

- STORE Rsrc, addr: Сохранение 8-битного значения из регистра Rsrc по адресу addr в памяти.

- LOAD_IMM Rdest, value: Загрузка немедленного значения value в регистр Rdest.

Команды управления потоком

- JUMP addr: Переход к команде по адресу addr.

- JZ addr: Переход к адресу addr, если флаг нуля (Z) установлен.

- JNZ addr: Переход к адресу addr, если флаг нуля (Z) не установлен.

- NOP: Нет операции (для задержки или синхронизации).

Регистр флагов (F)

Регистр флагов F имеет 8 бит, каждый из которых отвечает за определенное состояние процессора:

- Бит 0 (Z): Флаг нуля. Устанавливается, если результат последней арифметической операции равен нулю.

- Бит 1 (C): Флаг переноса. Устанавливается, если произошел перенос в результате сложения или заимствование при вычитании.

- Бит 2 (N): Флаг знака. Устанавливается, если результат операции отрицательный (для знаковых чисел).

- Бит 3 (V): Устанавливается, если произошел переполнение при арифметических операциях со знаковыми числами.

- Бит 4 (I): Флаг прерывания. Указывает, разрешены ли прерывания.

- Бит 5 (D): Флаг десятичного режима. Используется для операций с десятичными числами.

- Бит 6 (O): Флаг общего назначения (может использоваться для пользовательских нужд).

- Бит 7 (S): Флаг статуса. Может использоваться для других состояний процессора или для специальных операций.

еще вариант

Архитектура процессора

Регистры:

- R0, R1, R2, R3 — 4 регистра общего назначения.

- F — регистр флагов, который может содержать флаги, такие как Zero (Z), Carry (C), Overflow (O) и Negative (N).

- PC — регистр счетчика команд, который указывает на адрес следующей инструкции в памяти.

Память:

- Предполагается наличие памяти для хранения инструкций и данных. Можно использовать простую модель с адресацией по байтам.

Инструкции:

- LOAD R, addr — загрузка значения из памяти по адресу addr в регистр R.

- STORE R, addr — сохранение значения из регистра R в память по адресу addr.

- ADD R1, R2 — сложение значений из регистров R1 и R2 с сохранением результата в R1.

- SUB R1, R2 — вычитание значений из регистров R1 и R2 с сохранением результата в R1.

- JZ addr — переход по адресу addr, если флаг Zero установлен.

| Бит | Назначение | Описание |

|---|---|---|

| 0 | ZF | Флаг нуля. Устанавливается, если результат операции равен нулю. |

| 1 | CF | Флаг переноса. Устанавливается, если произошел перенос при арифметической операции. |

| 2 | OF | Флаг переполнения. Устанавливается, если результат операции выходит за пределы допустимого диапазона. |

| 3 | SF | Флаг знака. Устанавливается, если результат операции отрицательный. |

| 4 | PF | Флаг четности. Устанавливается, если количество единиц в результате операции четно. |

| 5 | AF | Флаг вспомогательного переноса. Используется в двоичных операциях. |

| 6 | DF | Флаг направления. Определяет направление работы с памятью (вперед или назад). |

| 7 | TF | Флаг трассировки. Используется для отладки, позволяет выполнять инструкции по одной. |

Примеры двух процов

Основная система команд Гигатрон

Книги

Токхайм Р. Микропроцессоры | Просмотр документа tokheim.pdf

Процессор выполнен на транзисторах в домашних условиях - тут

Build an 8-bit computer from scratch - тут

HABR Создание процессора с нуля для чайников - тут

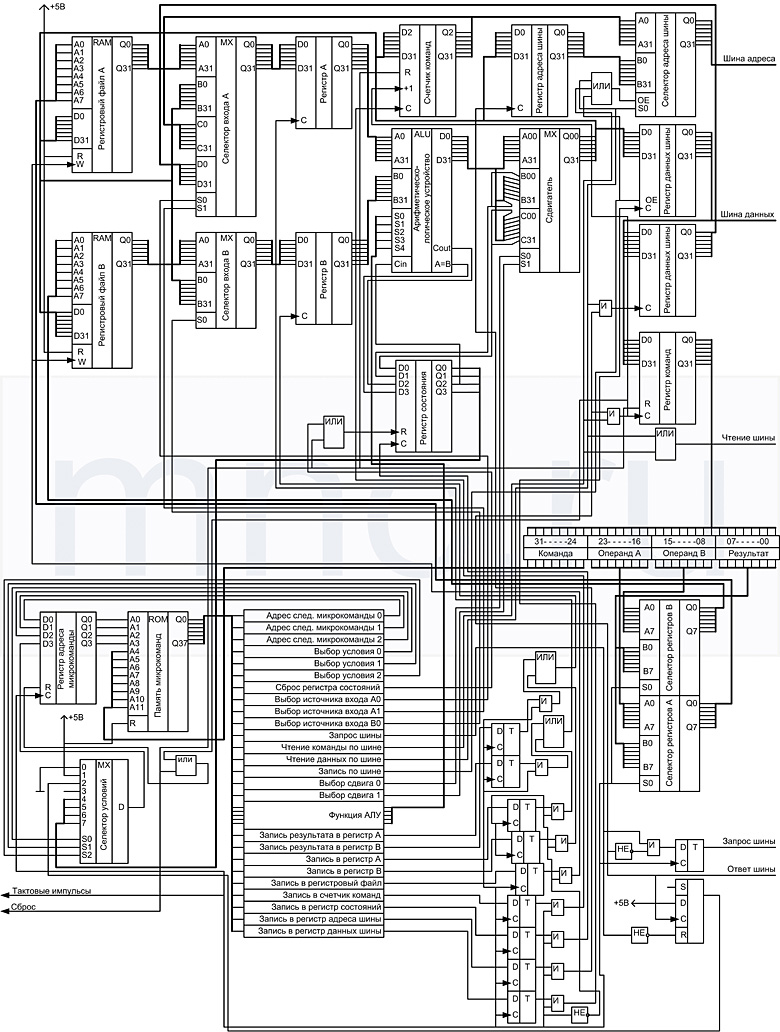

Подробная схема процессора

И вот теперь имеется в наличии вся необходимая информация, чтобы нарисовать подробную схему процессора со всеми вспомогательными элементами и со всеми управляющими сигналами. Выглядеть она будет примерно так:

Сразу необходимо упомянуть о некоторых особенностях этой схемы, не описанных раньше:

- Выбор адресов аргументов команды осуществляется при помощи тактового сигнала. В первой половине тактового периода, соответствующей выборке аргументов команды, выбраны регистры по адресам операндов А для одной копии регистрового файла, и В – для другой. Во второй половине периода, соответствующей выполнению операции и записи результата, в обеих копиях регистрового файла выбран регистр по адресу операнда С.

- Увеличение счетчика команд производится автоматически одновременно с записью в регистр команд, которая осуществляется по сигналу ответа шины при выполнении считывания команды из памяти. По этому же сигналу происходит сброс регистра адреса микрокоманды.

- Счетчик команд состоит из 30 разрядов, а не 32, поскольку команда состоит из четырех байтов, и должна размещаться в памяти, начиная с границы 32-разрядного слова, а не байта.

- При выполнении сдвига вправо или влево, крайний разряд переносится на освободившееся место, т.е. сдвиг всегда циклический. Кроме этого, разряд переноса записывается в соответствующий разряд регистра состояния.

Автор текста - Молчанов Н.Н.